Go to the source code of this file.

|

| enum | lpf_e {

INV_FILTER_256HZ_NOLPF2 = 0,

INV_FILTER_188HZ,

INV_FILTER_98HZ,

INV_FILTER_42HZ,

INV_FILTER_20HZ,

INV_FILTER_10HZ,

INV_FILTER_5HZ,

INV_FILTER_2100HZ_NOLPF,

NUM_FILTER

} |

| |

| enum | gyro_fsr_e {

INV_FSR_250DPS = 0,

INV_FSR_500DPS,

INV_FSR_1000DPS,

INV_FSR_2000DPS,

NUM_GYRO_FSR

} |

| |

| enum | clock_sel_e { INV_CLK_INTERNAL = 0,

INV_CLK_PLL,

NUM_CLK

} |

| |

| enum | accel_fsr_e {

INV_FSR_2G = 0,

INV_FSR_4G,

INV_FSR_8G,

INV_FSR_16G,

NUM_ACCEL_FSR

} |

| |

| enum | detectedMPUSensor_e {

MPU_NONE,

MPU_3050,

MPU_60x0,

MPU_60x0_SPI,

MPU_65xx_I2C,

MPU_65xx_SPI

} |

| |

| enum | mpu6050Resolution_e { MPU_HALF_RESOLUTION,

MPU_FULL_RESOLUTION

} |

| |

| #define MPU6500_WHO_AM_I_CONST (0x70) |

| #define MPU_INQUIRY_MASK 0x7E |

| #define MPU_RA_ACCEL_CONFIG 0x1C |

| #define MPU_RA_ACCEL_XOUT_H 0x3B |

| #define MPU_RA_ACCEL_XOUT_L 0x3C |

| #define MPU_RA_ACCEL_YOUT_H 0x3D |

| #define MPU_RA_ACCEL_YOUT_L 0x3E |

| #define MPU_RA_ACCEL_ZOUT_H 0x3F |

| #define MPU_RA_ACCEL_ZOUT_L 0x40 |

| #define MPU_RA_BANK_SEL 0x6D |

| #define MPU_RA_CONFIG 0x1A |

| #define MPU_RA_DMP_CFG_1 0x70 |

| #define MPU_RA_DMP_CFG_2 0x71 |

| #define MPU_RA_DMP_INT_STATUS 0x39 |

| #define MPU_RA_EXT_SENS_DATA_00 0x49 |

| #define MPU_RA_FF_DUR 0x1E |

| #define MPU_RA_FF_THR 0x1D |

| #define MPU_RA_FIFO_COUNTH 0x72 |

| #define MPU_RA_FIFO_COUNTL 0x73 |

| #define MPU_RA_FIFO_EN 0x23 |

| #define MPU_RA_FIFO_R_W 0x74 |

| #define MPU_RA_GYRO_CONFIG 0x1B |

| #define MPU_RA_GYRO_XOUT_H 0x43 |

| #define MPU_RA_GYRO_XOUT_L 0x44 |

| #define MPU_RA_GYRO_YOUT_H 0x45 |

| #define MPU_RA_GYRO_YOUT_L 0x46 |

| #define MPU_RA_GYRO_ZOUT_H 0x47 |

| #define MPU_RA_GYRO_ZOUT_L 0x48 |

| #define MPU_RA_I2C_MST_CTRL 0x24 |

| #define MPU_RA_I2C_MST_DELAY_CTRL 0x67 |

| #define MPU_RA_I2C_MST_STATUS 0x36 |

| #define MPU_RA_I2C_SLV0_ADDR 0x25 |

| #define MPU_RA_I2C_SLV0_CTRL 0x27 |

| #define MPU_RA_I2C_SLV0_DO 0x63 |

| #define MPU_RA_I2C_SLV0_REG 0x26 |

| #define MPU_RA_I2C_SLV1_ADDR 0x28 |

| #define MPU_RA_I2C_SLV1_CTRL 0x2A |

| #define MPU_RA_I2C_SLV1_DO 0x64 |

| #define MPU_RA_I2C_SLV1_REG 0x29 |

| #define MPU_RA_I2C_SLV2_ADDR 0x2B |

| #define MPU_RA_I2C_SLV2_CTRL 0x2D |

| #define MPU_RA_I2C_SLV2_DO 0x65 |

| #define MPU_RA_I2C_SLV2_REG 0x2C |

| #define MPU_RA_I2C_SLV3_ADDR 0x2E |

| #define MPU_RA_I2C_SLV3_CTRL 0x30 |

| #define MPU_RA_I2C_SLV3_DO 0x66 |

| #define MPU_RA_I2C_SLV3_REG 0x2F |

| #define MPU_RA_I2C_SLV4_ADDR 0x31 |

| #define MPU_RA_I2C_SLV4_CTRL 0x34 |

| #define MPU_RA_I2C_SLV4_DI 0x35 |

| #define MPU_RA_I2C_SLV4_DO 0x33 |

| #define MPU_RA_I2C_SLV4_REG 0x32 |

| #define MPU_RA_INT_ENABLE 0x38 |

| #define MPU_RA_INT_PIN_CFG 0x37 |

| #define MPU_RA_INT_STATUS 0x3A |

| #define MPU_RA_MEM_R_W 0x6F |

| #define MPU_RA_MEM_START_ADDR 0x6E |

| #define MPU_RA_MOT_DETECT_CTRL 0x69 |

| #define MPU_RA_MOT_DETECT_STATUS 0x61 |

| #define MPU_RA_MOT_DUR 0x20 |

| #define MPU_RA_MOT_THR 0x1F |

| #define MPU_RA_PRODUCT_ID 0x0C |

| #define MPU_RA_PWR_MGMT_1 0x6B |

| #define MPU_RA_PWR_MGMT_2 0x6C |

| #define MPU_RA_SIGNAL_PATH_RESET 0x68 |

| #define MPU_RA_SMPLRT_DIV 0x19 |

| #define MPU_RA_TEMP_OUT_H 0x41 |

| #define MPU_RA_TEMP_OUT_L 0x42 |

| #define MPU_RA_USER_CTRL 0x6A |

| #define MPU_RA_WHO_AM_I 0x75 |

| #define MPU_RA_WHO_AM_I 0x75 |

| #define MPU_RA_WHO_AM_I_LEGACY 0x00 |

| #define MPU_RA_X_FINE_GAIN 0x03 |

| #define MPU_RA_XA_OFFS_H 0x06 |

| #define MPU_RA_XA_OFFS_L_TC 0x07 |

| #define MPU_RA_XG_OFFS_TC 0x00 |

| #define MPU_RA_XG_OFFS_USRH 0x13 |

| #define MPU_RA_XG_OFFS_USRL 0x14 |

| #define MPU_RA_Y_FINE_GAIN 0x04 |

| #define MPU_RA_YA_OFFS_H 0x08 |

| #define MPU_RA_YA_OFFS_L_TC 0x09 |

| #define MPU_RA_YG_OFFS_TC 0x01 |

| #define MPU_RA_YG_OFFS_USRH 0x15 |

| #define MPU_RA_YG_OFFS_USRL 0x16 |

| #define MPU_RA_Z_FINE_GAIN 0x05 |

| #define MPU_RA_ZA_OFFS_H 0x0A |

| #define MPU_RA_ZA_OFFS_L_TC 0x0B |

| #define MPU_RA_ZG_OFFS_TC 0x02 |

| #define MPU_RA_ZG_OFFS_USRH 0x17 |

| #define MPU_RA_ZG_OFFS_USRL 0x18 |

| #define MPU_RA_ZRMOT_DUR 0x22 |

| #define MPU_RA_ZRMOT_THR 0x21 |

| #define MPU_RF_DATA_RDY_EN (1 << 0) |

| #define MPUx0x0_WHO_AM_I_CONST (0x68) |

| typedef bool(* mpuReadRegisterFunc)(uint8_t reg, uint8_t length, uint8_t *data) |

| typedef bool(* mpuWriteRegisterFunc)(uint8_t reg, uint8_t data) |

| Enumerator |

|---|

| INV_FSR_2G |

|

| INV_FSR_4G |

|

| INV_FSR_8G |

|

| INV_FSR_16G |

|

| NUM_ACCEL_FSR |

|

| Enumerator |

|---|

| INV_CLK_INTERNAL |

|

| INV_CLK_PLL |

|

| NUM_CLK |

|

| Enumerator |

|---|

| MPU_NONE |

|

| MPU_3050 |

|

| MPU_60x0 |

|

| MPU_60x0_SPI |

|

| MPU_65xx_I2C |

|

| MPU_65xx_SPI |

|

| Enumerator |

|---|

| INV_FSR_250DPS |

|

| INV_FSR_500DPS |

|

| INV_FSR_1000DPS |

|

| INV_FSR_2000DPS |

|

| NUM_GYRO_FSR |

|

| Enumerator |

|---|

| INV_FILTER_256HZ_NOLPF2 |

|

| INV_FILTER_188HZ |

|

| INV_FILTER_98HZ |

|

| INV_FILTER_42HZ |

|

| INV_FILTER_20HZ |

|

| INV_FILTER_10HZ |

|

| INV_FILTER_5HZ |

|

| INV_FILTER_2100HZ_NOLPF |

|

| NUM_FILTER |

|

| Enumerator |

|---|

| MPU_HALF_RESOLUTION |

|

| MPU_FULL_RESOLUTION |

|

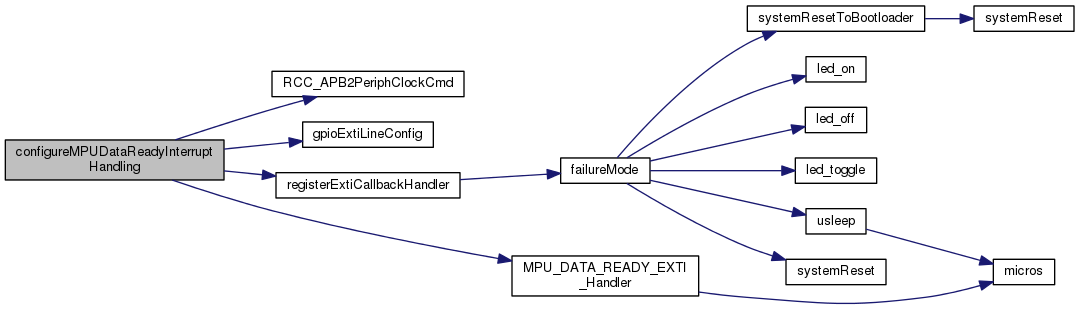

| void configureMPUDataReadyInterruptHandling |

( |

void |

| ) |

|

| bool mpuAccRead |

( |

int16_t * |

accData | ) |

|

| bool mpuGyroRead |

( |

int16_t * |

gyroADC | ) |

|

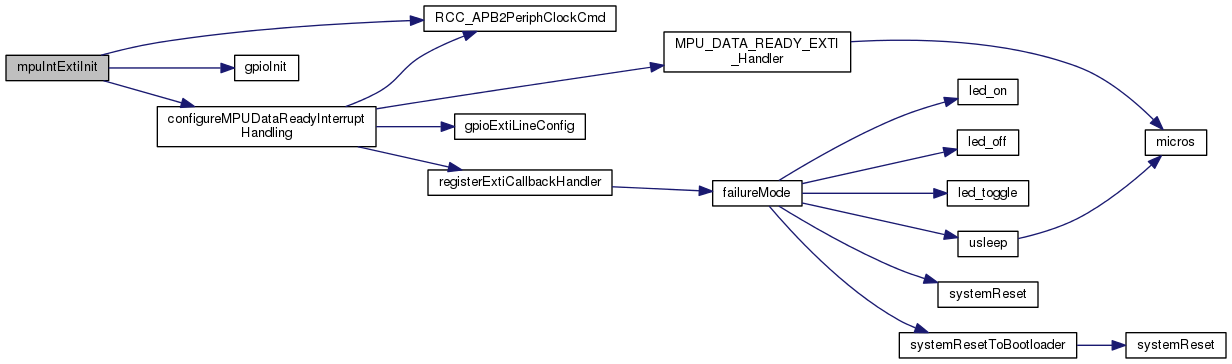

| void mpuIntExtiInit |

( |

void |

| ) |

|

| bool mpuIsDataReady |

( |

void |

| ) |

|